## Characterizing and Filtering out Device Noise for Quantum Optimization Algorithms

**Optimization in Quantum Computing DARPA Project Number: W911NF2010022**

Muqing Zheng and Xiu Yang Industrial and Systems Engineering, Lehigh University Tamás Terlaky (PI) muz219@lehigh.edu

**Research Objective:**

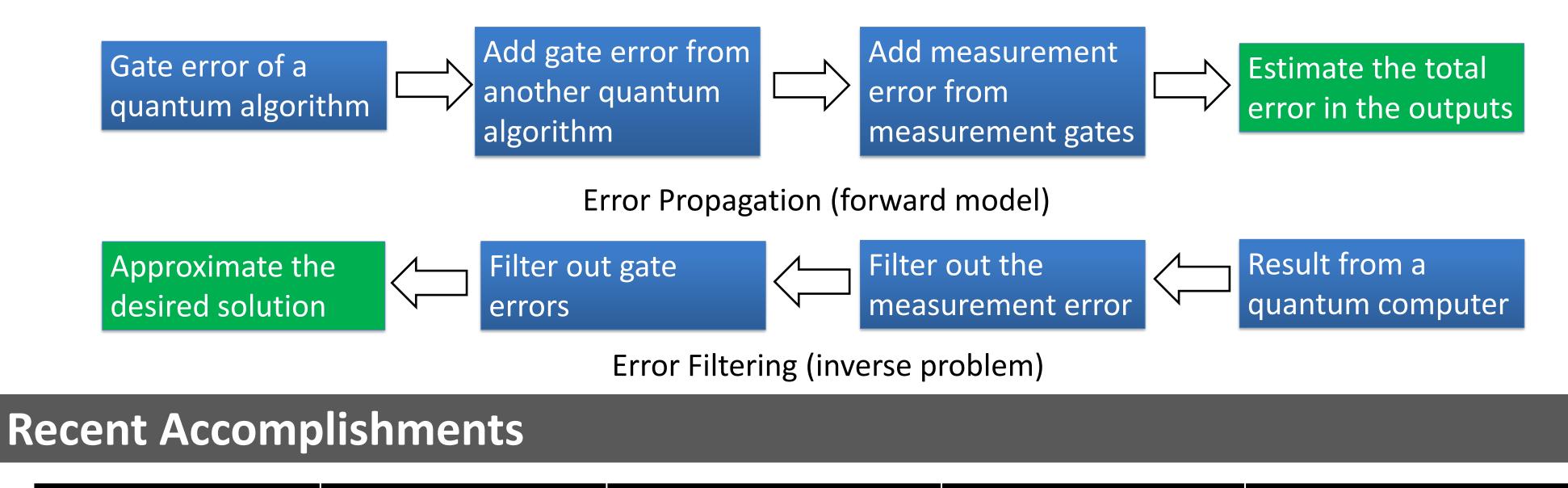

Error propagation and filtering models for optimization algorithms.

Pr(Meas. 0) after 200 Entangled 3-Oubit State 2-Oubit Grover's **Correct Solutions Prob**

| Source or Method    | NOT Gates | Tomography Fidelity | Search Solution Prob. | of 4-Qubit QAOA |

|---------------------|-----------|---------------------|-----------------------|-----------------|

| Ideal/Simulator     | 1         | 1                   | 1                     | 0.8930          |

| Raw Data            | 0.6377    | 0.6974              | 0.6727                | 0.5784          |

| Qiskit              | N/A       | 0.8863              | 0.7097                | 0.5968          |

| QDT                 | N/A       | N/A                 | 0.7107                | 0.6400          |

| Consistent Bayesian | 1.0000    | 0.9443              | 0.9128                | 0.6975          |

We use the *consistent Bayesian method* [1] to capture the **fluctuations** of Ο quantum hardware error parameters, such as gate error rates and readout error rates.

Inference for gate errors uses the following error propagation model. Ο

$$\tilde{p}(x) = \sum_{s \in \{0,1\}^n} \left[ (1-\epsilon)^{|s|} \right]^m \hat{p}(s)(-1)^{s.x}$$

Law of total probability is considered to predict readout errors. Ο

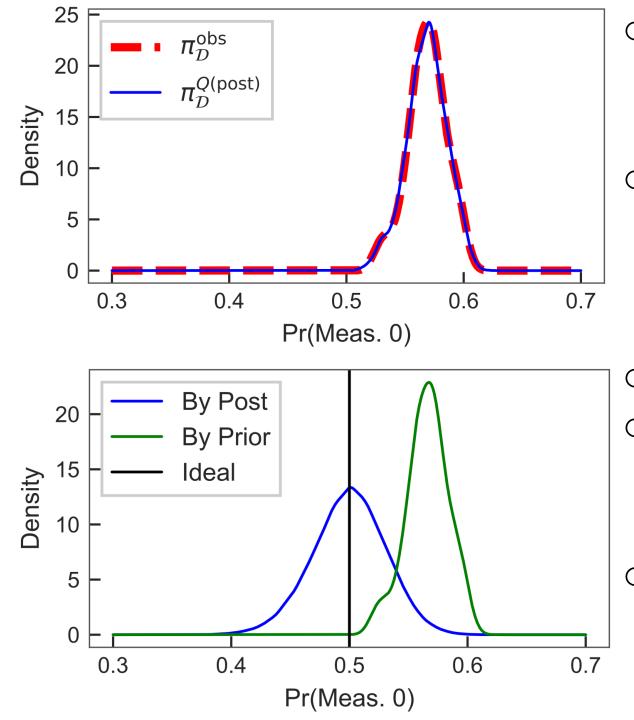

Posterior distributions of error parameters can perfectly simulate the noise Ο in data (figure in the upper left) and denoise the training data (figure in the lower left).

Our approach has better performance than two existing methods in several Ο experiments conducted on IBM's quantum computer (table above and more in [2]).

## **Looking Forward**

## Develop a correlated readout error model using the polynomial number of parameters.

Expand gate error model to a more complicated situation.  $\bullet$

## Build up a description of hardware errors from an integrated quantum circuit perspective.

[1] T. Butler, J. Jakeman, and T. Wildey. Combining push-forward measures and bayes' rule to construct consistent solutions to stochastic inverse problems. SIAM Journal on Scientific Computing, 40(2):A984–A1011, January 2018. DOI: 10.1137/16m1087229. [2] Zheng, M., Li, A., Terlaky, T., & Yang, X. (2020). A bayesian approach for characterizing and mitigating gate and measurement errors. arXiv preprint arXiv:2010.09188.